#### <u>UNIT – I</u>

### **IC FABRICATION**

IC classification - fundamental of monolithic IC technology - epitaxial growth - masking and etching - diffusion of impurities - Realisation of monolithic ICs and packaging - Fabrication of diodes - capacitance, resistance, FETs and PV cell.

#### Part – A – 2Mark Questions

#### 1. Define an Integrated circuit.

An integrated circuit(IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

#### 2. Give the difference between monolithic and hybrid ICs.

| Monolithic IC's                  |            |          |             | Hybrid IC's                                     |                                                |

|----------------------------------|------------|----------|-------------|-------------------------------------------------|------------------------------------------------|

| Monolithi                        | c IC's are | those in | which trans | istors,                                         | Hybrid IC's are those in which elements are of |

| diodes,                          | resistors  | are      | fabricated  | and                                             | discrete form and others are connected on the  |

| interconnected on the same chip. |            |          | ip.         | chip with discrete elements externally to those |                                                |

| -                                |            |          |             | formed on the chip.                             |                                                |

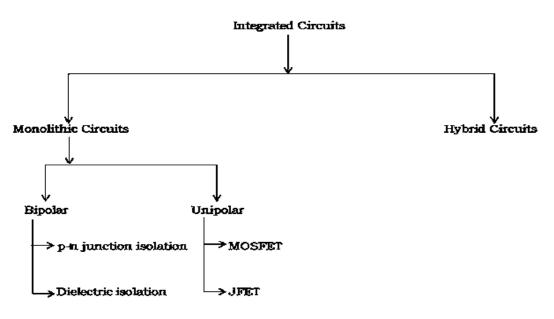

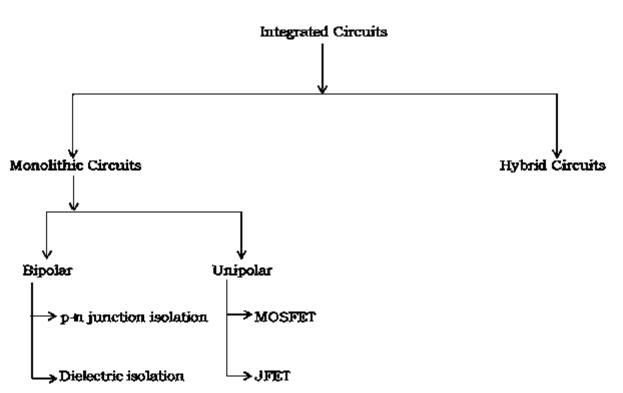

## 3. Classify IC. (Dec – 14, 15) Or Classify ICs based on the manufacturing techniques. Nov/Dec 2019.

#### 4. List the steps used for preparation of silicon wafer. Nov/Dec 2019.

- $\rightarrow$  The silicon wafer process can be subdivided into number of sub processes as follows:

- i. Slicing crystal Ingots

- ii. Ingot trimming and grinding

- iii. Ingot slicing

- iv. Wafer etching

- v. Wafer polishing

- vi. Wafer cleaning

#### 5. What is lithography?[May-17, 18]

→ The process of photolithography makes it possible to produce microscopically small circuit and device pattern on Si wafer.

- $\rightarrow$  Two processes are involved in photolithography namely,

- Making a photographic mask

- Photo etching

- $\rightarrow$  The prime use of photolithography in IC manufacturing is to selectively etch or remove the SiO<sub>2</sub> layer.

- 6. What are the advantages of integrated circuits over discrete circuits?(May 06,15) (Dec 14, 16) or Name any two merits of ICs. Nov/Dec 2019.

## Advantages of integrated circuits:

- $\rightarrow$  Miniaturization and hence increased equipment density.

- $\rightarrow\,$  Cost reduction due to batch processing.

- $\rightarrow$  Increased system reliability due to the elimination of soldered joints.

- $\rightarrow$  Improved functional performance.

- $\rightarrow$  Matched devices.

- $\rightarrow$  Increased operating speeds. Reduction in power consumption

## 7. What are the differences between diffusion and ion implantation?

| Diffusion                                                                                                                                                                                                                                    | Ion Implantation                                                                                                                                                                                                                                                           |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $\rightarrow$ The process of introducing impurities into                                                                                                                                                                                     | $\rightarrow$ This is a process of introducing dopants into                                                                                                                                                                                                                |

| selected regions of a silicon wafer is called                                                                                                                                                                                                | selected areas of the surface of the wafer by                                                                                                                                                                                                                              |

| diffusion.                                                                                                                                                                                                                                   | bombarding the surface with high-energy                                                                                                                                                                                                                                    |

| $\rightarrow$ The rate at which various impurities diffuse                                                                                                                                                                                   | ions of the particular dopant.                                                                                                                                                                                                                                             |

| into the silicon will be of the order of $1\mu$ m/hr at the temperature range of $900^{\circ}$ C to $1100^{\circ}$ C. Therefore, the impurity atoms have the tendency to move from regions of higher concentrations to lower concentrations. | <ul> <li>→It is performed at low temperature. Therefore, previously diffused regions have a lesser tendency for lateral spreading.</li> <li>→In ion implantation process, accelerating potential &amp; beam content are dielectrically controlled from outside.</li> </ul> |

| $\rightarrow$ In diffusion process, temperature has to be                                                                                                                                                                                    |                                                                                                                                                                                                                                                                            |

| controlled over a large area inside the oven.                                                                                                                                                                                                |                                                                                                                                                                                                                                                                            |

## 8. What is the purpose of oxidation process in IC Fabrication?

- → The process of oxidation consists of growing a thin film of silicon dioxide on the surface of the silicon wafer.

- $\rightarrow$  Silicon dioxide plays an important role in shielding of the surface so that dopant atoms, by diffusion or ion implantation, may be driven into other selected regions.

- $\rightarrow$  SiO<sub>2</sub> is an extremely hard protective coating & is unaffected by almost all reagents except by hydrochloric acid. Thus it stands against any contamination.

# 9. What is meant by ion implantation? Why is it preferred over diffusion process? (May – 06, 14, 15) (Dec – 12)

- $\rightarrow$  This is a process of introducing dopants into selected areas of the surface of the wafer by bombarding the surface with high-energy ions of the particular dopant.

- $\rightarrow$  It is performed at low temperature. Therefore, previously diffused regions have a lesser tendency for lateral spreading.

- $\rightarrow$  The ion implantation process is preferred over diffusion because of the following reasons:

- i. The degree of uniformity is maintained same from wafer to wafer.

- ii. The layer can be formed anywhere within substrate.

- iii. The lateral spread is very small.

- iv. The impurity concentration is highly uniform over the wafer.

#### 10. Write the basic chemical reaction in the epitaxial growth process of pure silicon.

$\rightarrow$  The basic chemical reaction in the epitaxial growth process of pure silicon is the hydrogen reduction of silicon tetrachloride.

#### 1200°C

$SiCl_4 + 2H_2 < ----> Si + 4 HCl$

#### 11. List the basic process used in IC fabrication.

- $\rightarrow$  The fabrication of a monolithic transistor includes the following steps.

- 1. Epitaxial growth

- 2. Oxidation

- 3. Photolithography

- 4. Isolation diffusion

- 6. Emitter diffusion

- 7. Contact mask

- 8. Aluminium metallization

- 9. Passivation

5. Base diffusion

#### 12. What is parasitic capacitance? (Dec - 04)

- $\rightarrow$  In the p-n junction isolation technique, the components on the chip are isolated by forming isolation p-n junction islands.

- $\rightarrow$  There are two back to back p-n junction diodes which are under reverse biased condition.

- $\rightarrow$  So such reverse bias presents an undesirable and unavoidable capacitance across it.

- $\rightarrow$  This is called parasitic capacitance.

- $\rightarrow$  This is undesirable as it limits high frequency performance of the circuit.

#### 13. What are the popular IC packages available? (Dec – 03, 06, 13, 15)

- 1. Metal can package

- 2. Dual-in-line package

- 3. Ceramic flat package

## 14. What is meant by dielectric isolation in I.C Fabrication? Mention its application and Limitations. (Dec - 03)

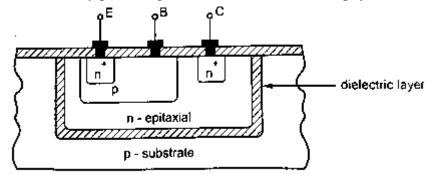

$\rightarrow$  In dielectric isolation, a layer of solid dielectric such as SiO<sub>2</sub> or ruby completely surrounds each components thereby producing isolation, both electrical & physical.

#### Limitations:

$\rightarrow$  This method is very expensive due to additional processing steps needed.

#### **Applications:**

- $\rightarrow$  This is mostly used for fabricating IC's required for special application in military and aerospace.

- $\rightarrow$  It is also possible to fabricate both p-n-p &n-p-n transistors within the same silicon substrate.

#### 15. How surface layer of $SiO_2$ is formed? (Dec – 04)

- $\rightarrow$  The surface layer of SiO<sub>2</sub> is formed by oxidation process. In general, thermal oxidation technique is preferred practically to grow thin oxide layers.

- $\rightarrow$  Other techniques used are vapour phase oxidation and plasma anodization.

## **16.** What is meant by substantial diffusion? (May – 05)

- $\rightarrow$  The process of adding impurities to the silicon chip at very high temperature is called substantial diffusion.

- 17. What is the need for buried layer in fabrication of monolithic integrated transistor? (Dec 07) (Dec 14)

- $\rightarrow$  The buried layer is used in integrated transistor to decrease the collector series resistance. It provides low resistivity current path.

### $\rightarrow$ The buried n+ layer shunts the n-epitaxial collector layer effectively, decreasing the resistance.

## 18. Differentiate between thin film and thick film technology in IC fabrication. (Dec - 07)

- $\rightarrow$  Generally thick-thin film ICs are used to produce only passive elements.

- $\rightarrow$  The thick film technology is comparatively easier and inexpensive while the thin film technology is slightly complicated and expensively.

- $\rightarrow$  The thin film technology produces components with greater precision as compared to those produced by the thick film technology.

## 19. List the advantages of thin film resistor. [Apr/May 2019]

Thin film is usually used for precision applications.

- $\rightarrow$  High Tolerances

- → Low Temperature Coefficients

- $\rightarrow$  Low Noise

## 20. Define the term epitaxial growth.

- $\rightarrow$  Epitaxial means growing a mono-crystalline film on top of a mono-crystalline surface.

- → Thus Epitaxial is a crystalline growth process in which the foundation layer i.e. substrate works as a seed crystal.

## 21. What do you mean by Monolithic process? (Dec – 06)

$\rightarrow$  The process in which all the active as well as passive elements or components along with their interconnections are manufactured on a single silicon crystal is known as monolithic process.

## 22. What is meant by hybrid ICs?

- $\rightarrow$  The hybrid ICs are the integrated circuits used for high power application.

- $\rightarrow$  The hybrid ICs may combine two or more monolithic ICs or combine monolithic ICs with thick-thin film IC in one single package.

## 23. What is meant by planar technology?

- $\rightarrow$  The fabrication of different discrete devices such as diodes, transistors and integrated circuits is carried out by the same technology.

- $\rightarrow$  The various processes involved in the fabrication of different devices are carried out in a single plane. Hence this is also referred as a planar technology.

## 24. Name the parameters which govern the thickness of the film in the oxidation process. (Dec -05)

- → The main important parameter which governs the thickness of the film in the Oxidation process is Temperature.

- $\rightarrow$  This is because, to grow the oxide layer, high temperature is to be maintained.

- $\rightarrow$  The other important parameters which govern the thickness of the film in the Oxidation process are time till which the process is to be carried out and the moisture contents.

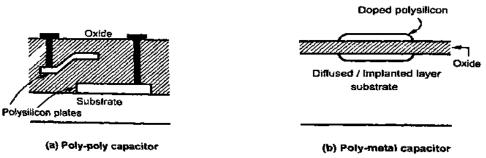

# 25. How are capacitors fabricated in ICs? Draw the cross-sectional view of M0S capacitor. (May - 07)

- $\rightarrow$  The common parallel plate capacitor structures area shown in the Fig.

- → In most widely used type shown in Fig. (a), the two poly-silicon plates are separated by silicon dioxide (SiO<sub>2</sub>).

- $\rightarrow$  Here the lower plate rests on the top of the Substrate.

- $\rightarrow\,$  The capacitor shown in Fig. (b) is MOS capacitor.

- $\rightarrow$  It consists of an implanted or diffused heavily doped layer within substrate while a poly-silicon or metal plate on the top of a thin oxide layer.

$\rightarrow$  For MOS capacitors, generally gate oxide is used with no extra processing step.

Capacitor structures

#### 26. What are the limitations of Integrated Circuits? (May – 07) (Nov-16, 17)

- $\rightarrow$  The disadvantage if ICs are,

- i. The capacitors more than 30 pF cannot be fabricated.

- ii. The resistors more than  $100 \text{ k}\Omega$  cannot be fabricated.

- iii. The coils or inductors cannot be fabricated.

- iv. The ICs can handle limited amount of power.

- v. The ICs function at low voltages.

#### 27. Explain the importance of SiO<sub>2</sub> layer. (May – 06)

- $\rightarrow$  In the planar process it is essential to protect certain regions of surface of the wafer so that the dopant atoms may be driven into other selective regions during the processes such as diffusion or ion implantation.

- $\rightarrow$  For such shielding purpose, silicon dioxide (SiO<sub>2</sub>) is best suited.

- 28. In the Czochralski crystal growth process under what gas does crystal pulling carried out? (May 05)

- $\rightarrow$  In general, during Czochralski crystal growth process, the gas used is argon.

- 29. What is the advantage of using dry etching process? (May 05)

- $\rightarrow$  The major advantage of using the dry etching process over wet etching process is that it is possible to achieve smaller openings of thickness  $\leq 1 \mu m$ .

#### **30.** What is the step taken to avoid material defect in ion implantation? (May – 05)

$\rightarrow$  To avoid the material defect in the ion implantation process, the depth of penetration must be controlled appropriately by the acceleration energy of the incident beam and the doping concentration.

#### 31. Distinguish between dry etching and wet etching. (May-15)

Wet etching process, the chemical reagents are used are liquid form. Dry etching process, it is achieve smaller line openings compared to wet process.

#### 32. What are the advantages of plasma etching? (Nov-13)

It is possible to achieve smaller line openings compared to wet process.

#### 33. Define Encapsulation. [Apr/May 2019]

In electronics manufacturing, integrated circuit packaging is the final stage of semiconductor device fabrication, in which the block of semiconductor material is encapsulated in a supporting case that prevents physical damage and corrosion.

## <u>UNIT – I</u>

### IC FABRICATION

## Part - B - 16Mark Questions

### **FUNDAMENTALS OF MONOLITHIC IC TECHNOLOGY**

#### **Integrated Circuits:**

An integrated circuit (IC) is a miniature, low cost electronic circuit consisting of active and passive components fabricated together on a single crystal of silicon. The active components are transistors and diodes and passive components are resistors and capacitors.

#### Advantages of integrated circuits:

- $\rightarrow$  Miniaturization and hence increased equipment density.

- $\rightarrow$  Cost reduction due to batch processing.

- $\rightarrow$  Increased system reliability due to the elimination of soldered joints.

- $\rightarrow$  Improved functional performance.

- $\rightarrow$  Matched devices.

- $\rightarrow$  Increased operating speeds.

- $\rightarrow$  Reduction in power consumption.

#### 1. Write short notes on classification of IC.

#### **<u>1. IC Classification:</u>**

- $\rightarrow$  Integrated circuits can be classified into analog, digital and mixed signal (both analog and digital on the same chip).

- → Based upon above requirement two different IC technologies namely Monolithic Technology and Hybrid Technology have been developed.

- $\rightarrow$  In monolithic IC, all circuit components, both active and passive elements and their interconnections are manufactured into or on top of a single chip of silicon.

- $\rightarrow$  In hybrid circuits, separate component parts are attached to a ceramic substrate and interconnected by means of either metallization pattern or wire bounds.

- $\rightarrow$  Digital integrated circuits can contain anything from one to millions of logic gates, flip-flops, multiplexers, and other circuits in a few square millimetres.

- → The small size of these circuits allows high speed, low power dissipation, and reduced manufacturing cost compared with board-level integration.

- $\rightarrow$  These digital ICs, typically microprocessors, DSPs, and micro controllers work using binary mathematics to process "one" and "zero" signals.

- → Analog ICs, such as sensors, power management circuits, and operational amplifiers, work by processing continuous signals. They perform functions like amplification, active filtering, demodulation, mixing, etc.

- → Analog ICs ease the burden on circuit designers by having expertly designed analog circuits available instead of designing a difficult analog circuit from scratch.

- → ICs can also combine analog and digital circuits on a single chip to create functions such as A/D converters and D/A converters.

- $\rightarrow$  Such circuits offer smaller size and lower cost, but must carefully account for signal interference.

#### **<u>1.1 Classification of ICs:</u>**

#### **<u>1.2 Generations:</u>** SSI, MSI and LSI

- → The first integrated circuits contained only a few transistors. Called "Small-Scale Integration" (SSI), digital circuits containing transistors numbering in the tens provided a few logic gates for example, while early linear ICs such as the Plessey SL201 or the Philips TAA320 had as few as two transistors.

- → The term Large Scale Integration was first used by IBM scientist Rolf Landauer when describing the theoretical concept, from there came the terms for SSI, MSI, VLSI, and ULSI. They began to appear in consumer products at the turn of the decade, a typical application being FM inter-carrier sound processing in television receivers.

- → The next step in the development of integrated circuits, taken in the late 1960s, introduced devices which contained hundreds of transistors on each chip, called "Medium-Scale Integration" (MSI).

- → They were attractive economically because while they cost little more to produce than SSI devices, they allowed more complex systems to be produced using smaller circuit boards, less assembly work (because of fewer separate components), and a number of other advantages.

#### VLSI

- $\rightarrow$  The final step in the development process, starting in the 1980s and continuing through the present, was "very large-scale integration" (VLSI).

- $\rightarrow$  The development started with hundreds of thousands of transistors in the early 1980s, and continues beyond several billion transistors as of 2007.

- → In 1986 the first one megabit RAM chips were introduced, which contained more than one million transistors.

- → Microprocessor chips passed the million transistor mark in 1989 and the billion transistor mark in 2005 ULSI, WSI, SOC and 3D-IC.

- → To reflect further growth of the complexity, the term ULSI that stands for "Ultra-Large Scale Integration" was proposed for chips of complexity of more than 1 million transistors.

- → Wafer-scale integration (WSI) is a system of building very-large integrated circuits that uses an entire silicon wafer to produce a single "super-chip".

- → Through a combination of large size and reduced packaging, WSI could lead to dramatically reduced costs for some systems, notably massively parallel supercomputers.

- → The name is taken from the term Very-Large-Scale Integration, the current state of the art when WSI was being developed.

- → System-on-a-Chip (SoC or SOC) is an integrated circuit in which all the components needed for a computer or other system is included on a single chip.

- $\rightarrow$  The design of such a device can be complex and costly, and building disparate components on a single piece of silicon may compromise the efficiency of some elements.

- → However, these drawbacks are offset by lower manufacturing and assembly costs and by a greatly reduced power budget, because signals among the components are kept on-die, much less power are required.

- → Three Dimensional Integrated Circuits (3D IC) has two or more layers of active electronic components that are integrated both vertically and horizontally into a single circuit.

- → Communication between layers uses on-die signalling, so power consumption is much lower than in equivalent separate circuits.

- $\rightarrow$  Judicious use of short vertical wires can substantially reduce overall wire length for faster operation.

## 2. FUNDAMENTAL OF MONOLITHIC IC TECHNOLOGY 2.1 WAFER PREPARATION

## 2. Describe the steps of crystal growth and wafer preparation in detail. (May - 05) (4)

- → The most important process in IC fabrication is the formation of a silicon wafer through crystal growth.

- $\rightarrow$  This process can be subdivided into number of sub processes as follows:

- vii. Slicing crystal Ingots

- viii. Ingot trimming and grinding

- ix. Ingot slicing

- x. Wafer etching

- xi. Wafer polishing

- xii. Wafer cleaning

## 1. <u>Slicing Crystal Ingots:</u>

- $\rightarrow$  The important semiconductor material for the fabrication of semiconductor devices and integrated circuits is **silicon**.

- $\rightarrow$  Other semiconductor materials are **germanium** and **gallium arsenide**.

- $\rightarrow$  At present 95% of the semiconductor devices and integrated circuits are manufactured using silicon only and for very special applications gallium arsenide is preferred.

- $\rightarrow$  It is seen that the bipolar junction transistor (BJT) was developed first in 1948, with germanium as a basic semiconductor material.

- $\rightarrow$  But it was observed that silicon is better option than germanium.

- $\rightarrow$  The comparison between silicon and germanium is as given in Table.

| Sl. No. | Germanium                                                  | Silicon                                           |  |  |

|---------|------------------------------------------------------------|---------------------------------------------------|--|--|

| 1.      | It is unsuitable for certain application                   | It is comparatively suitable for all              |  |  |

|         | due to high junction leakage currents                      | applications as junction leakage currents are     |  |  |

|         | as it has currents relatively narrow                       | negligible as the energy band gap is              |  |  |

|         | energy band gap (0.66 eV). comparatively broader (1.1 eV). |                                                   |  |  |

| 2.      | Germanium devices can be operated                          | Silicon devices can be operated till 200°C        |  |  |

|         | till 100°C temperatures.                                   | temperatures.                                     |  |  |

| 3.      | Germanium oxides are unsuitable for                        | Silicon dioxides are the most wanted for the      |  |  |

|         | certain device applications.                               | planar processes.                                 |  |  |

| 4.      | The intrinsic resistivity without any                      | The intrinsic resistivity Without any dopantis    |  |  |

|         | dopantis 47 $\Omega$ cm, hence not suitable                | 230,000 $\Omega$ cm, hence most suitable for high |  |  |

|         | for high voltage rectifying devices.                       | voltage rectifying devices as well as infrared    |  |  |

|         |                                                            | sensing devices.                                  |  |  |

| 5.      | Germanium is costlier as compared to                       | Silicon is cheaper as compared to                 |  |  |

|         | Silicon.                                                   | Germanium.                                        |  |  |

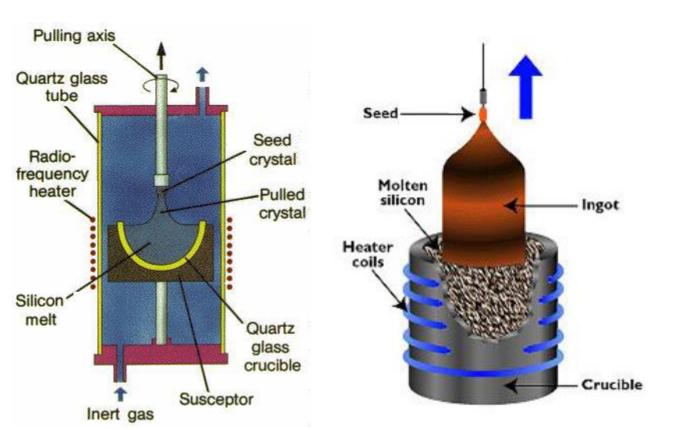

$\rightarrow$  The primary method of the crystal growth is Czochralski (CZ) method.

$\rightarrow$  In practice all the silicon required for integrated circuits is prepared by using this method only.

- → In general, a phase change from solid, liquid or gas phases to crystalline solid phase is nothing but growing crystal.

- → Czochralski method is used for silicon crystal growth from which ultimately silicon wafers are produced.

- $\rightarrow$  The apparatus used for the crystal growth is called Czochralski crystal growth apparatus or puller.

- → The puller has four important subsystems namely furnace, crystal pulling mechanism, ambient control and control systems.

- $\rightarrow$  The simplified version of Czochralski crystal puller is as shown:

- $\rightarrow$  The furnace consists of a crucible, crucible support, rotation mechanism and heating element housed in a chamber.

- $\rightarrow$  The crucible is made up of fused silica (SiO<sub>2</sub>) as this material is chemically un reactive with molten silicon.

- $\rightarrow$  An EGS block is heated in a fused silica crucible with the appropriate dopant using a heating element.

- $\rightarrow$  The material in the crucible is heated to a temperature which is greater than the melting point of silicon, i.e. 1417°C.

- $\rightarrow$  A resistance heating is preferred for large pullers; while induction heating is used for small melt sizes.

- $\rightarrow$  Then a small single crystal rod of silicon is immersed into the molten material.

- $\rightarrow$  This rod is called seed crystal. This seed crystal is located at the crystal pulling assembly.

- $\rightarrow$  In this assembly, using rotating mechanism seed shaft and seed chuck are rotated.

- $\rightarrow$  Lowering the seed crystal in molten silicon allows the crystal ingot to form on the seed by solidification.

- $\rightarrow$  The main function of crystal pulling assembly is to control the pull rate of seed crystal and crystal rotation both, with minimum Vibrations and precision.

- → During the crystal growth, the crystal is rotated slowly, by stirring the molten and averaging out temperature gradients leading to inhomogeneous solidification.

- $\rightarrow$  To get the ingots of circular cross-section, the crucible and the seed crystal are rotated in opposite direction.

- → When the seed crystal is pulled out of the molten material, due to solidification, silicon ingot gets formed exactly same as seed crystal.

- $\rightarrow$  In general, the diameter is controlled by the pull rate.

- $\rightarrow$  The standard diameter of the ingot is about 150 mm and the length is about 2 m.

- $\rightarrow$  The ingot with such dimensions weighs about 60 kg.

- $\rightarrow$  The silicon growth is generally conducted in a vacuum or in an inert gas like helium or argon.

- $\rightarrow$  To control the process parameters such as temperature, crystal diameter, pull rate and rotation speed etc, control system is used which works under either open loop control or closed loop control.

## 2. Ingot trimming and grinding:

- $\rightarrow$  First of all, the seed which initiated the crystal growth is separated from the circular ingot.

- → The top and bottom ends are also cut off. As silicon is hard and brittle material, industrial grade diamond is used for shaping and cutting it.

- → This process is called ingot trimming. After completion of the crystal growth, it is generally tested for resistivity and perfection evaluation.

- $\rightarrow$  So the portions of the ingot failed in the above tests are also cut.

- $\rightarrow$  Note that these cuttings can be recycled for new crystal growth after cleaning.

- $\rightarrow$  After trimming of the ingot, the surface grinding of the ingot is carried out.

- $\rightarrow$  Actually the ingots are slightly oversized. Hence with the help of lathe like diamond tool, the ingot is ground to a precise diameter.

- $\rightarrow$  After grinding the ingot to a precise diameter, generally two flats are ground along the length of the ingot.

- $\rightarrow$  The larger flat is called major or primary flat and it is positioned relative to the crystal direction.

- $\rightarrow$  The X-ray technique is used to locate the primary flat.

- → The primary flat is very important as,

i) It serves for mechanical alignment of the wafer in automatic processing, and

ii) It serves for orienting ICs on the wafer relative to the crystal.

- → The smaller flat is called **secondary** flat which is used to identify the orientation (< 100 > or < 111 >) and conductivity (p or n) of the wafer.

## 3. Ingot slicing:

- $\rightarrow$  After completing ingot trimming and grinding process, the ingot is ready for next process i.e. ingot slicing.

- $\rightarrow$  The slices of the ingot are called wafers and typically the thickness of wafer may vary from 0.4 mm to 1 mm.

- $\rightarrow$  This process is very important as it is necessary to maintain the flat plane and desired surface orientations.

- $\rightarrow$  The slicing also determines the orientation of the surface. Generally, there are two orientations <100> and <111>.

- $\rightarrow$  The wafers with <100> are cut 'on orientations' and wafers with <111>are cut 'off orientations'.

- $\rightarrow$  The ingot is sliced using a circular cutting blade kept in tension on the outer edge while having the cutting edge on the inner diameter.

- $\rightarrow$  The thickness of the wafer is determined by the slicing.

- $\rightarrow$  It is another important wafer parameter because thicker wafers can easily withstand the stresses of subsequent thermal processes.

- $\rightarrow$  The higher quality of slicing is achieved by using capacitive sensing device near the blade which helps the blade to be positioned correctly to achieve exactly flat plane cut.

## 4. Wafer etching:

- → If the sliced wafers are to be used for VLSI application, then before etching process two sided mechanical lapping process is carried out.

- $\rightarrow$  Using this process, wafers with uniform flatness are achieved which are mostly required for photolithography.

- $\rightarrow$  Due to the machining operations during trimming, grinding and slicing, the surface and edges of the wafers get contaminated and even damaged.

- $\rightarrow$  The depth of damage depends on the mechanical operations carried previously.

- $\rightarrow\,$  It is observed that the damaged and contaminated regions are not more than 10  $\mu m$  deep.

- $\rightarrow$  Even by using chemical etching process, all the damaged and contaminated edges can be removed.

- $\rightarrow$  Practically mixture of hydrofluoric, acetic and nitric acids is used in chemical etching. This is called acidic etching.

- $\rightarrow$  The other alternative is to use alkaline etching using potassium hydroxide or sodium hydroxide.

- $\rightarrow$  By the etching process, typically 10 µm to 30 µm of wafer is removed from both the sides.

## 5. <u>Wafer polishing:</u>

- $\rightarrow$  After etching, the wafer is polished to eliminate the micro-cracks and debris.

- $\rightarrow$  The main intension of polishing a wafer is to provide a smooth and perfect flat surface such that the device features can be engraved.

- $\rightarrow$  The polishing is done with the help of a polishing machine. Note that the polishing process removes further 10 µm to 30 µm of the wafer surface typically.

- $\rightarrow$  The three steps of lapping, etching and polishing reduce the wafer thickness by 40 to 150  $\mu$ m.

- $\rightarrow$  Thus by considering the typical figures, to have the wafer of 200 µm thickness, the thickness of the substrate required is 560 µm.

- $\rightarrow$  In practice, the processed 6 inch wafers are typically 250 µm to 500 µm thick.

## 6. <u>Wafer cleaning:</u>

- $\rightarrow$  The silicon wafers are cleaned using chemicals.

- $\rightarrow$  Generally organic films, heavy metals are deposited on the surface of the wafers.

- $\rightarrow$  Hence by using HCl H<sub>2</sub>0<sub>2</sub> aqueous solution, metallic impurities can be removed.

- $\rightarrow$  First the wafer is cleaned by using HCl H<sub>2</sub>O<sub>2</sub>. Then wafer is rinsed in water to deionise.

- $\rightarrow$  Again the wafer is dipped in hydrofluoric acid. Then again the wafer is rinsed in water.

- $\rightarrow$  After cleaning process, the wafer is ready for the formation of the dies.

**3.** Explain the basic Process used in silicon planar technology with neat diagram. (Nov-17) (16, 13)

## Or

Describe the methods of thin thick film technologies [Apr/May 2019]

## Or

Explain the basic processes used in the fabrication of monolithic ICs. (Dec - 12) (16)

## Or

Discuss with necessary diagram, the basic process for fabrication of ICs using silicon IC planar technology. Nov/Dec 2019. (13)

## **2.2 CONSTRUCTION OF A MONOLITHIC BIPOLAR TRANSISTOR:**

- $\rightarrow$  The fabrication of a monolithic transistor includes the following steps:

- 1. Epitaxial growth

- 2. Oxidation

- 3. Photolithography

- 4. Diffusion

- i. Isolation diffusion

- ii. Base diffusion

- iii. Emitter diffusion

- 5. Ion implantation

- 6. Isolation Technique

- 7. Contact mask

- 8. Aluminium metallization

- 9. Passivation

→ The letters P and N in the figures refer to type of doping, and a minus (-) or plus (+) with P and N indicates lighter or heavier doping respectively.

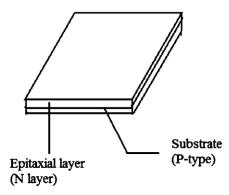

## 2.2.1 EPITAXIAL GROWTH

4. Explain the epitaxy and explain epitaxial growth process. (Dec – 03, 06, 10, 13, 16) (4, 6, 8) Or

Explain the process of epitaxial growth in IC fabrication process with neat diagram. (May -07, 15) (8)

#### 1. Epitaxial growth:

- $\rightarrow$  Epitaxy means growing a single crystal silicon structure upon an original silicon substrate, so that the resulting layer is an extension of the substrate crystal structure.

- $\rightarrow$  The basic chemical reaction in the epitaxial growth process of pure silicon is the hydrogen reduction of silicon tetrachloride.

#### 1200°C

#### $SiCl_4+2H_2<--->Si+4~HCl$

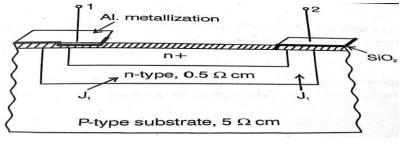

- $\rightarrow$  The first step in transistor fabrication is creation of the collector region.

- $\rightarrow$  It normally requires a low resistivity path for the collector current.

- $\rightarrow$  This is due to the fact that, the collector contact is normally taken at the top, thus increasing the collector series resistance and the V<sub>CE(Sat)</sub> of the device.

- $\rightarrow$  The higher collector resistance is reduced by a process called buried layer as shown in figure.

- $\rightarrow$  In this arrangement, a heavily doped N region is sandwiched between the N-type epitaxial layer and P type substrate.

- $\rightarrow$  This buried N+ layer provides a low resistance path in the active collector region to the collector contact C.

- $\rightarrow$  In effect, the buried layer provides a low resistance shunt path for the flow of current.

- → For fabricating an NPN transistor, we begin with a P-type silicon substrate having a resistivity of typically 1Ω-cm, corresponding to an acceptor ion concentration of  $1.4 \times 10^{15}$  atoms/cm<sup>3</sup>.

- $\rightarrow$  An oxide mask with the necessary pattern for buried layer diffusion is prepared.

- $\rightarrow$  This is followed by masking and etching the oxide in the buried layer mask.

- $\rightarrow$  The N-type buried layer is now diffused into the substrate.

- $\rightarrow$  A slow-diffusing material such as arsenic or antimony is used, so that the buried layer will stay-put during subsequent diffusions.

- $\rightarrow$  The junction depth is typically a few microns, with sheet resistivity of around 20 $\Omega$  per square.

- → Then, an epitaxial layer of lightly doped N-silicon is grown on the P-type substrate by placing the wafer in the furnace at  $1200^{\circ}$  C and introducing a gas containing phosphorus (donor impurity).

- $\rightarrow$  The subsequent diffusions are done in this epitaxial layer.

- $\rightarrow$  All active and passive components are formed on the thin N-layer epitaxial layer grown over the P-type substrate.

## 5. Explain the importance of SiO<sub>2</sub> layer. (May – 06) (8)

Or

### Describe the steps of oxidation in IC fabrication. (May - 05) (4)

## 2.2.2 Oxidation:

→ The process of oxidation consists of growing a thin film of silicon dioxide on the surface of the silicon wafer at  $1000^{\circ}$  C.

Si + 2HO----->  $SiO_2 + 2H_2$

- $\rightarrow$  Silicon dioxide plays an important role in shielding of the surface so that dopant atoms, by diffusion or ion implantation, may be driven into other selected regions.

- → SiO2 is an extremely hard protective coating & is unaffected by almost all reagents except by hydrochloric acid. Thus it stands against any contamination.

## 2.2.3 MASKING AND ETCHING

1. Explain the process of masking and photo-etching in IC fabrication. (Dec - 07) (7) (Dec - 14, 16) (6, 13)

Or What is photolithography? What is the purpose of diffusion? (Dec – 13, 14) (8) [Apr/May 2019] Or

Explain in detail about photo-lithography. (Dec – 03, 16) (May – 05) (4, 7)

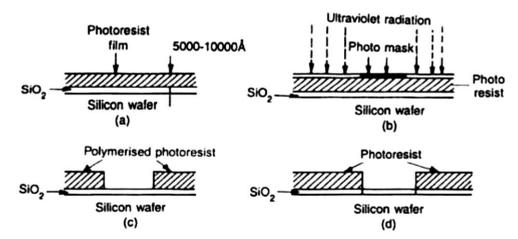

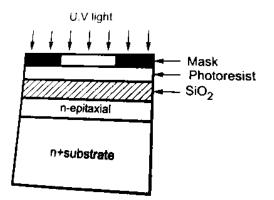

## Photolithography:

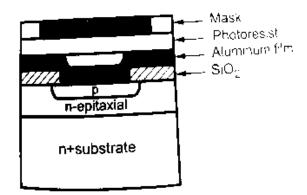

- → The prime use of photolithography in IC manufacturing is to selectively etch or remove the SiO<sub>2</sub> layer.

- $\rightarrow$  As shown in figure, the surface of the oxide is first covered with a thin uniform layer of photosensitive emulsion (Photo resist).

- $\rightarrow$  The mask, a black and white negative of the required pattern, is placed over the structure.

- $\rightarrow$  When exposed to ultraviolet light, the photo resist under the transparent region of the mask becomes polymerized.

- → The mask is then removed and the wafer is treated chemically that removes the unexposed portions of the photo resist film.

- $\rightarrow$  The polymerized region is cured so that it becomes resistant to corrosion.

- $\rightarrow$  Then the chip is dipped in an etching solution of hydrofluoric acid which removes the oxide layer not protected by the polymerized photoresist.

- $\rightarrow$  This creates openings in the SiO<sub>2</sub> layer through which P-type or N-type impurities can be diffused using the isolation diffusion process as shown in figure.

- $\rightarrow$  After diffusion of impurities, the polymerized photoresist is removed with sulphuric acid and by a mechanical abrasion process.

#### **2.2.4 DIFFUSION OF IMPURITIES**

#### 7. Explain in detail about diffusion process in IC fabrication. (Dec - 06) (8)

#### **2.2.4.1 Isolation Diffusion:**

- $\rightarrow$  The integrated circuit contains many devices.

- $\rightarrow$  Since a number of devices are to be fabricated on the same IC chip, it becomes necessary to provide good isolation between various components and their interconnections.

- $\rightarrow$  The most important techniques for isolation are:

- 1. PN junction Isolation

- 2. Dielectric Isolation

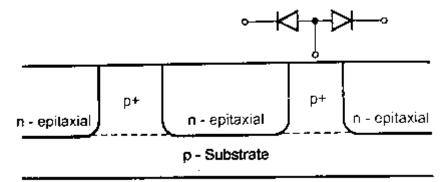

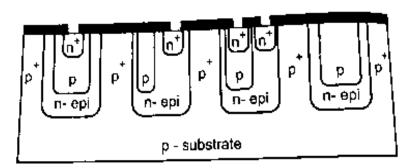

- → In PN junction isolation technique, the P+ type impurities are selectively diffused into the N-type epitaxial layer so that it touches the P-type substrate at the bottom.

- $\rightarrow$  This method generated N-type isolation regions surrounded by P-type moats.

- $\rightarrow$  If the P-substrate is held at the most negative potential, the diodes will become reversebiased, thus providing isolation between these islands.

- $\rightarrow$  The individual components are fabricated inside these islands.

- $\rightarrow$  This method is very economical, and is the most commonly used isolation method for general purpose integrated circuits.

- $\rightarrow$  In dielectric isolation method, a layer of solid dielectric such as silicon dioxide or ruby surrounds each component and this dielectric provides isolation.

- $\rightarrow$  The isolation is both physical and electrical.

- → This method is very expensive due to additional processing steps needed and this is mostly used for fabricating IC's required for special application in military and aerospace.

- $\rightarrow$  The PN junction isolation diffusion method is shown in figure. The process takes place in a furnace using boron source.

- $\rightarrow$  The diffusion depth must be at least equal to the epitaxial thickness in order to obtain complete isolation.

- $\rightarrow$  Poor isolation results in device failures as all transistors might get shorted together.

- $\rightarrow$  The N-type island shown in figure forms the collector region of the NPN transistor.

- $\rightarrow$  The heavily doped P-type regions marked P+ are the isolation regions for the active and passive components that will be formed in the various N-type islands of the epitaxial layer.

#### 2.2.4.2 Base diffusion:

- $\rightarrow$  Formation of the base is a critical step in the construction of a bipolar transistor.

- $\rightarrow$  The base must be aligned, so that, during diffusion, it does not come into contact with either the isolation region or the buried layer.

- → Frequently, the base diffusion step is also used in parallel to fabricate diffused resistors for the circuit.

- $\rightarrow$  The value of these resistors depends on the diffusion conditions and the width of the opening made during etching.

- $\rightarrow$  The base width influences the transistor parameters very strongly. Therefore, the base junction depth and resistivity must be tightly controlled.

- → The base sheet resistivity should be fairly high (200- 500 $\Omega$  per square) so that the base does not inject carriers into the emitter.

- $\rightarrow$  For NPN transistor, the base is diffused in a furnace using a boron source.

- → The diffusion process is done in two steps, pre deposition of dopants at 900<sup>0</sup> C and driving them in at about  $1200^{0}$  C.

- $\rightarrow$  The drive-in is done in an oxidizing ambience, so that oxide is grown over the base region for subsequent fabrication steps.

- $\rightarrow$  Figure shows that P-type base region of the transistor diffused in the N-type island (collector region) using photolithography and isolation diffusion processes.

## 2.2.4.3 Emitter Diffusion:

- $\rightarrow$  Emitter Diffusion is the final step in the fabrication of the transistor.

- $\rightarrow$  The emitter opening must lie wholly within the base.

- $\rightarrow$  Emitter masking not only opens windows for the emitter, but also for the contact point, which provides a low resistivity ohmic contact path for the emitter terminal.

- → The emitter diffusion is normally a heavy N-type diffusion, producing low-resistivity layer that can inject charge easily into the base.

- $\rightarrow$  A Phosphorus source is commonly used so that the diffusion time id shortened and the previous layers do not diffuse further.

- $\rightarrow$  The emitter is diffused into the base, so that the emitter junction depth very closely approaches the base junction depth.

- $\rightarrow$  The active base is then a P-region between these two junctions which can be made very narrow by adjusting the emitter diffusion time.

- $\rightarrow$  Various diffusion and drive in cycles can be used to fabricate the emitter. The Resistivity of the emitter is usually not too critical.

- $\rightarrow$  The N-type emitter region of the transistor diffused into the P-type base region is shown below.

- $\rightarrow$  However, this is not needed to fabricate a resistor where the resistivity of the P-type base region itself will serve the purpose.

- $\rightarrow$  In this way, an NPN transistor and a resistor are fabricated simultaneously.

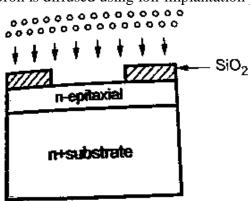

## 8. Explain in detail about ion implantation in IC fabrication. (Dec – 03) (6)

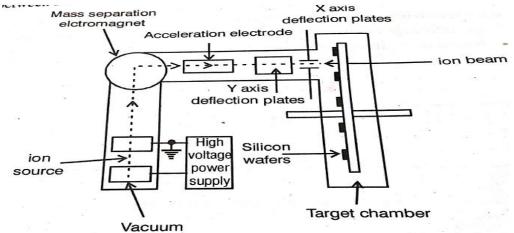

## **2.5. Ion implantation technique:**

- $\rightarrow$  It is another technique to introduce impurities into a silicon wafer.

- → In this process silicon wafer are placed in a vacuum chamber, and are scanned by a beam of high energy ions. (boron for p- type, phosphorus for n- type)

- $\rightarrow$  These ions are accelerated by energies between 20 kV to 259 kV.

- $\rightarrow$  These ions strike the silicon wafers, they penetrate some distance into wafer.

- $\rightarrow$  The depth of any penetration of any particular type of ion increasing accelerating voltage.

- $\rightarrow$  It is performed at low temperature. Therefore, previously diffused regions have a lesser tendency for lateral spreading.

- $\rightarrow$  In diffusion process, temperature has to be controlled over a large area inside the oven, where as in ion implantation process, accelerating potential & beam content are dielectrically controlled from outside.

Fig 2.5 Ion implantation

## 2.5.1 Advantages of Ion Implantation:

1. Doping levels can be precisely controlled since the incident ion beam can be accurately measured as an electric current.

2. The depth of the dopant can be easily regulated by control of the incident ion velocity. It is capable of very shallow penetrations.

3. Extreme purity of the dopant is guaranteed.

4. The doping uniformity across the surface can be accurately controlled.

5. Because the ions enter the solid as a directed beam, there is very little spread of the beam, thus the doping area can be clearly defined.

6. Since this is a low-temperature process, the movement of impurities is minimized.

9. Explain the importance of isolation and discuss the different methods of isolation. (May – 07)

(6)

Or

Describe in detail any two isolation techniques used to provide isolation between various components in IC fabrication with illustration. (May - 14) (16)

## 2.6. ISOLATION TECHNIQUES:

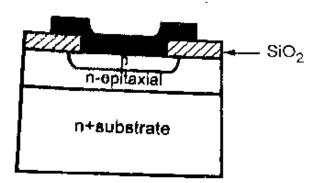

## 2.6.1 p-n junction isolation:

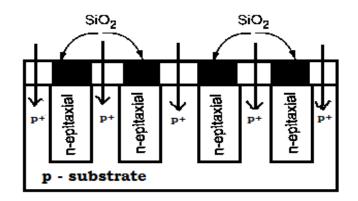

$\rightarrow$  Consider a p-substrate with n-type epitaxial layer grown over it.

$\rightarrow$  To provide isolation, a p-type impurity with high concentration is diffused selectively into an epitaxial layer such that it reaches to the p-substrate as shown below.

## p-n junction isolation technique

- $\rightarrow$  From the fig. it is clear that n-epitaxial region forms a region which is surrounded by p-type regions.

- $\rightarrow$  This region is called **island**.

- $\rightarrow$  Two regions are connected back-to-back and these two back-to-back diodes serve as **isolation** regions if both are reverse biased.

- $\rightarrow$  The main advantage of p-n junction isolation is that different components can be fabricated within the isolation islands.

- $\rightarrow$  But the disadvantage is the presence of undesirable and unavoidable parasitic capacitances at the islands.

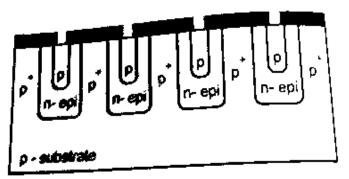

#### **2.6.2 Dielectric isolation:**

$\rightarrow$  In dielectric isolation, a layer of solid dielectric such as SiO<sub>2</sub> or ruby completely surrounds each components thereby producing isolation, both electrical & physical.

#### Dielectric isolation technique

- $\rightarrow$  This isolating dielectric layer is thick enough so that its associated capacitance is negligible.

- $\rightarrow$  Also, it is possible to fabricate both pnp& npn transistors within the same silicon substrate which is the main advantage of this technique.

- $\rightarrow$  But the disadvantage is the increase in cost. As the technique requires additional steps in fabrication to deposit a dielectric layer, this technique is expensive.

#### 2.7. CONTACT MASK:

- $\rightarrow$  After the fabrication of emitter, windows are etched into the N-type regions where contacts are to be made for collector and emitter terminals.

- $\rightarrow$  Heavily concentrated phosphorus N<sup>+</sup> dopant is diffused into these regions simultaneously.

- $\rightarrow$  The reason for the use of heavy N<sup>+</sup> diffusion is explained as follows:

- Aluminium, being a good conductor used for interconnection, is a P<sup>-</sup>type of impurity when used with silicon.

- Therefore, it can produce an unwanted diode or rectifying contact with the lightly doped N<sup>-</sup> material.

- Introducing a high concentration of N<sup>+</sup> dopant caused the Si lattice at the surface semimetallic.

- Thus the N<sup>+</sup> layer makes a very good ohmic contact with the Aluminium layer. This is done by the oxidation, photolithography and isolation diffusion processes.

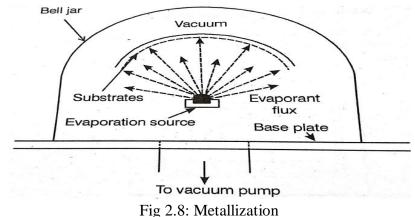

## 2.8. METALLIZATION:

- → The IC chip is now complete with the active and passive devices, and the metal leads are to be formed for making connections with the terminals of the devices.

- $\rightarrow$  Aluminium is deposited over the entire wafer by vacuum deposition. The thickness for single layer metal is 1µ m.

- → Metallization is carried out by evaporating aluminium over the entire surface and then selectively etching away aluminium to leave behind the desired interconnection and bonding pads as shown in figure.

- → Metallization is done for making interconnection between the various components fabricated in an IC and providing bonding pads around the circumference of the IC chip for later connection of wires.

## 2.9. PASSIVATION/ ASSEMBLY AND PACKAGING:

- $\rightarrow$  Metallization is followed by passivation, in which an insulating and protective layer is deposited over the whole device.

- $\rightarrow$  This protects it against mechanical and chemical damage during subsequent processing steps.

- → Doped or un doped silicon oxide or silicon nitride, or some combination of them, are usually chosen for passivation of layers.

- → The layer is deposited by chemical vapour deposition (CVD) technique at a temperature low enough not to harm the metallization.

10. Completely describe the various stages involved in the fabrication of an R, C and transistor in a single chip. (May – 05) (16) [Apr/May 2019]

Or

Describe briefly the various stages involved in the fabrication of IC. Draw the layout of a circuit by considering an example. (May - 07, 17] [Dec - 07, 15) (13, 10, 8)

Or

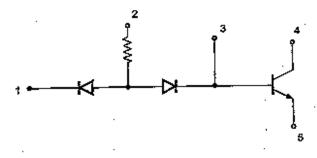

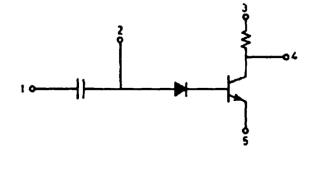

With the help of neat diagram explain the steps involved in the fabrication of the circuit shown in the Fig. using IC technology. (May - 04) (16)

Or

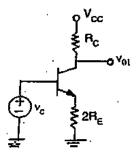

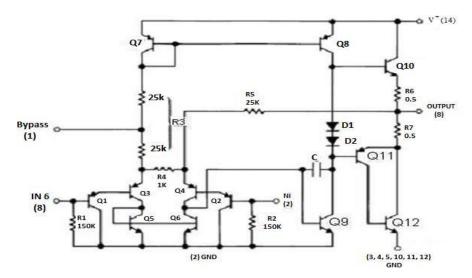

With respect to BJT based circuit given below, explain the various steps to implement the circuit into a monolithic IC. (Dec – 14)(May-17, 18) (13, 10)

## A. Preparation of Wafer:

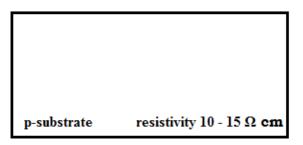

- $\rightarrow$  The starting material for the integrated circuit is p-type silicon which is called substrate.

- $\rightarrow$  Typically the thickness of the wafer ranges between 400 µm to 500 µm.

- $\rightarrow$  The diameter of the silicon wafer ranges between 100 mm to 200 mm.

- $\rightarrow$  For the acceptor concentration of 1.4×10<sup>15</sup> atoms/ cm<sup>3</sup> and the resistivity is 10 15  $\Omega$  cm.

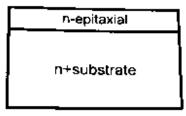

## **B. Epitaxial growth:**

- $\rightarrow$  Generally the doping types of the substrate and the epitaxial layer are opposite to provide isolation.

- → Thus n-type epitaxial layer is grown on p-type substrate which has resistivity of the order 1-2  $\Omega$  cm.

- $\rightarrow$  The epitaxial layer is useful as other components are fabricated within this layer.

- $\rightarrow$  This layer may act as an element of diode, diffused capacitor of collector of transistor.

| n-epitaxial layer | 1 - 5 Ω <b>cm</b> |

|-------------------|-------------------|

|                   |                   |

|                   |                   |

|                   |                   |

|                   |                   |

| p-substrate       | 5                 |

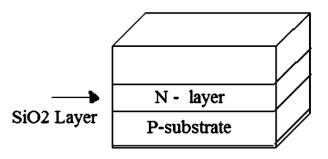

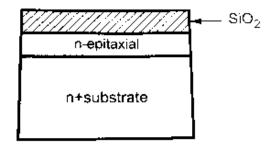

## C. Oxidation:

- $\rightarrow$  After the growth of an epitaxial layer, SiO<sub>2</sub> layer is grown on then-epitaxial layer.

- $\rightarrow$  This oxide layer is grown by using thermal oxidation method.

- $\rightarrow$  The thickness of the Si0<sub>2</sub>layer is smaller as compared to previous layers.

- $\rightarrow\,$  Typically it ranges between 0.05 to 2  $\mu m.$

| n-epitaxial layer |

|-------------------|

|                   |

|                   |

|                   |

|                   |

| p-substrate       |

|                   |

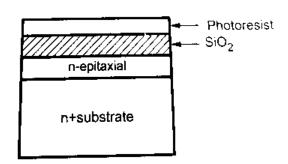

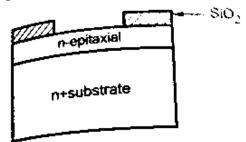

## **D. Lithographic process:**

$\rightarrow$  Then the wafer is coated with negative photoresist.

ma

- $\rightarrow$  To isolate the components of the circuit, p + type layer is diffused.

- $\rightarrow$  For this a opening has to be made using the proper mask. So proper mask is kept on a wafer and then U.V. light is passed.

- $\rightarrow$  After that it is photo-etched to get a wafer with openings for isolation diffusion.

| k |  |  |   |

|---|--|--|---|

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  |   |

|   |  |  | S |

## <u>E. Isolation diffusion using p – n junction Isolation technique</u>

- $\rightarrow$  After the lithographic process, from the openings from where SiO<sub>2</sub> is etched out, heavy doping of p-type is diffused for very long interval such that the impurities reach p-substrate penetrating n-type epitaxial layer.

- $\rightarrow$  Thus we get Isolation Island for four components.

- $\rightarrow$  Generally the concentration of acceptor atoms between the Isolation Islands is kept higher than p-substrate which ensures perfect electrical isolation.

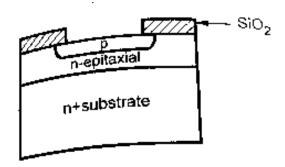

#### F. Base diffusion

- $\rightarrow$  After isolation diffusion once again a layer of SiO<sub>2</sub> is grown over a wafer and then using lithographic technique different pattern is marked on wafer to have opening for the diffusion of p-type impurity such as boron.

- $\rightarrow$  The impurity diffusion depth is controlled so that it cannot penetrate epitaxial layer to reach psubstrate.

- $\rightarrow$  This serves as base of transistor, anode of diode etc.

#### **G. Emitter diffusion**

- $\rightarrow$  After base diffusion, another set of window is required to diffuse n-type impurity for the capacitor, diode and transistor.

- $\rightarrow$  Hence again SiO<sub>2</sub> layer is grown on the wafer using different mask, new set of windows is opened using photo lithographic process.

- $\rightarrow$  Then through the new set of windows, n-type impurity e.g. phosphorous is diffused which forms the emitter of transistor and cathode of diode.

- $\rightarrow$  The windows are etched by using wet etching technique.

## H. Metallization

- $\rightarrow$  The final step in the process of IC fabrication is making interconnection using aluminium metal.

- $\rightarrow$  For this again wafer is grown with SiO<sub>2</sub> layer and using new photo-mask, new set of windows is opened at points from where terminals are to be brought out.

- $\rightarrow$  After the interconnections are made IC is subjected to the packaging process.

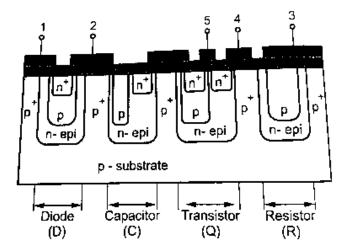

## **3. REALISATION OF MONOLITHIC IC'S AND PACKAGING**

11. Briefly explain the various types of IC packages. Mention the criteria for selecting an IC package. (May-15) (Nov-17)(13, 8)

#### 3.1 Packaging of ICs

- $\rightarrow$  After completing all the fabrication processes, several chips are ready on a wafer.

- $\rightarrow$  Each of the chips is nothing but a complete circuit. Now the next step is to separate out these chips and package them individually.

- $\rightarrow$  Using a diamond tipped tool, lines are scribed along the rectangular grids on the surface of the wafer.

- $\rightarrow$  The wafer is cut off along the lines drawn using the sharp diamond tipped tool.

- → Thus individual chips are separated from each other. Then each chip is assembled on a suitable package.

- $\rightarrow$  For comparing and assessing different packages, features are considered:

- (i) Maximum pin count

- (ii) Dimensions

- (iii) Pitch (spacing between the centres of adjacent pins)

- (iv) Encapsulating material (ceramic or plastic)

(v) Mode of mounting (plated through hole - TH or surface mount - SM)

- (vi) Maximum power dissipation.

- $\rightarrow$  For TH mounting DIP (dual in line package) and PGA (pin grid array) are the only standard packages.

- → For small scale integration (SSI) and medium scale integration (MSI),the different packages available are SIP (single in-line package), ZIP (zig-zag-in-line package) and QIPC (quad-in-line package) with TH mounting type.

- $\rightarrow$  For low pin counts the packages available are SO (small out-line package), SSOP (Shrunk small out-line package). Both these are with SM mounting type.

- → With SM mounting types there are two more packages namely chip carrier and TQFP(thin quad flat pack).

- $\rightarrow$  The chip carrier uses either plastic or ceramic as encapsulating material. The TQFP has very low profile and small weight.

| $\rightarrow$ The following table gives the different package types with their abbreviations. |                      |  |  |  |

|-----------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Package Type                                                                                  | Abbreviation         |  |  |  |

| Dual-in-line                                                                                  | DIP                  |  |  |  |

| Small outline                                                                                 | SO <sub>1</sub> SOIC |  |  |  |

| Shrunk small outline package                                                                  | SSOP                 |  |  |  |

| Single-in-line                                                                                | SIP                  |  |  |  |

| Zigzag-in-line                                                                                | ZIP                  |  |  |  |

| Quad-in-line                                                                                  | QIP                  |  |  |  |

| Plastic leaded chip carrier                                                                   | PLCC                 |  |  |  |

| Leadless ceramic chip carrier                                                                 | LCCC                 |  |  |  |

| Leadless chip carrier                                                                         | LLCC or LCC          |  |  |  |

| Leaded chip carrier                                                                           | LDCC                 |  |  |  |

| Flat pack                                                                                     | FP                   |  |  |  |

| Quad flat pack                                                                                | QFP                  |  |  |  |

| Ceramic Quad flat pack                                                                        | CQFP                 |  |  |  |

| Plastic Quad flat pack                                                                        | PQFP                 |  |  |  |

| Thin Quad flat pack                                                                           | TQFP                 |  |  |  |

| Pin grid array                                                                                | PGA                  |  |  |  |

| Plastic Pin grid array                                                                        | PPGA                 |  |  |  |

| Ceramic Pin grid array                                                                        | CPGA                 |  |  |  |

$\rightarrow$  The following table gives the different package types with their abbreviations.

| Package Type   | Pin Count Range | Mounting type |

|----------------|-----------------|---------------|

| Dual-in-line   | 8-64            | ТН            |

| Single-in-line | 5 - 40          | ТН            |

| Zigzag-in-line | 14 - 28         | TH            |

| Quad-in-line   | 14 - 64         | ТН            |

| Small outline  | 8-32            | SM            |

| Chip Carrier   | 16 - 200        | SM            |

| Flat pack      | 10 - 300        | SM            |

| Pin grid array | 68 - 500        | SM            |

12. With neat sketches explain the fabrication of diodes and capacitors.

Or

Explain the various methods of fabricating diodes in monolithic integrated circuits. (Dec -05, Dec -03) (May-18) (10, 13, 16)

Or

Discuss briefly about the fabrication methods of diodes and transistors. (Dec - 13) (16)

Or

Discuss the different ways to fabricate diodes. (Dec - 07) (Dec - 14) (10)

Or

Explain in step-by-step basis the fabrication of planar p-n junction diode with illustrations. (May -14) (8)

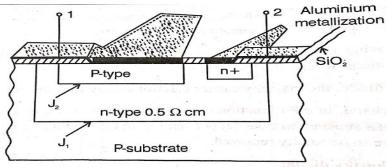

## 4. FABRICATION OF DIODES, CAPACITANCE, RESISTANCE, FETS AND PV CELL

## 4.1 Diode Fabrication:

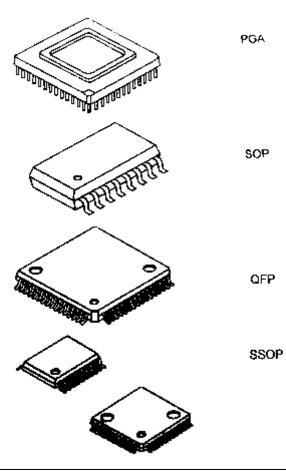

- $\rightarrow$  Diodes are used extensively in the integrated circuits for various applications such as digital applications.

- $\rightarrow$  Note that in the integrated circuits, a p-n junction diode is formed from the bipolar transistor.

- → Generally any two terminals of the transistor are connected together to get one terminal of diode, while the remaining terminal of the transistor serves as the second terminal of diode.

- $\rightarrow$  Different transistor connections to utilize it as a diode are as shown in the Fig. below.

- $\rightarrow$  Depending upon desired circuit performance and application, diode connection is selected.

- $\rightarrow$  The diode represented in Fig. (a) is used in digital circuits for high speed applications because of its lowest storage time and lowest forward voltage drop.

- $\rightarrow$  The diodes represented in Fig. (b) and (e) are used as stored charged devices.

- $\rightarrow$  The diodes represented in Fig. (c) and (d) have highest breakdown voltage.

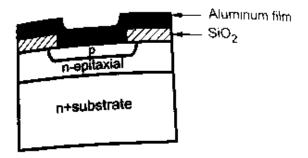

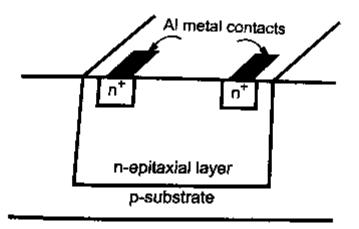

- 4.1.1Fabrication of a planar p-n junction diode is illustrated as follows:

- The starting material for the planar p-n junction diode is n+ substrate which is grown by using Czochralski growing process. The substrate is about 150 µm thick.

Using epitaxial growth process, layer of n-type silicon is deposited on the substrate. The layer is about 1 to 5 μm thick.

♦ Using oxidation process, Silicon dioxide (SiO<sub>2</sub>) is deposited.

✤ The surface is then coated with positive photoresist.

Appropriate mask is placed over the positive photoresist layer. It is properly aligned and then exposed to the ultraviolet light.

Then the mask is removed and photoresist is removed. Using etching process, only silicon dioxide layer under the exposed resist is etched.

✤ Then to form p-region, boron is diffused using ion-implantation process.

Boron diffuses in silicon easily, but not in SiO<sub>2</sub>. The resulting p-region is defined by the oxide opening. The Width of p-region is slightly greater than the oxide opening because of lateral doping during dopant diffusion.

Using Metallization, thin film of aluminium is deposited.

Then the metalized area is covered with photoresist. Another mask is placed over photoresist which ensures areas of metal to be preserved.

The wafer is then etched to remove unwanted metal. The photoresist is then dissolved. The contact metal is deposited on the back surface and using heat treatment ohmic contacts are made.

## 13. Explain how a monolithic capacitor can be fabricated. (Dec – 14) (6)

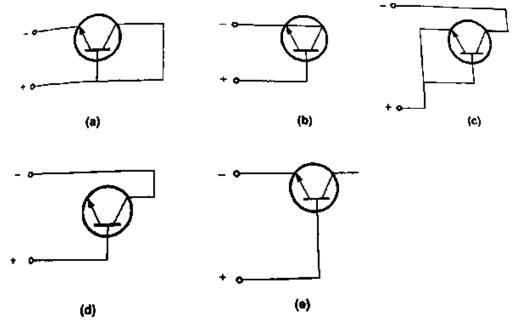

## 4.2 Capacitor Fabrication:

- → Monolithic capacitors are not frequently used in IC since they are limited in the range of values obtained and their performance.

- $\rightarrow$  Two common methods used for obtaining integrated capacitors are:

- Junction capacitor

- MOS and thin film capacitor

## **4.2.1 JUNCTION CAPACITOR**

- → The capacitor is formed by reverse- biased junction j2 which separates the epitaxial n- type layer from the upper p- type diffusion area.

- → However parasitic capacitance c is inevitable due to the junction, j1 between n- type epitaxial layer and substrate. Also series resistance results due to bulk resistance of n- region.

Fig 4.2.1 Junction capacitor

## **4.2.2 MOS AND THIN FILM CAPACITOR**

- $\rightarrow$  It is basically a parallel plate capacitor with SiO<sub>2</sub> as dielectric.

- $\rightarrow$  The heavily doped n<sup>+</sup> region formed during emitter diffusion forms lower plate and thin film of aluminium metallization for upper plate of capacitor with Sio<sub>2</sub> as dielectric.

Fig 4.2.2 MOS capacitor

14. Explain the various methods used for fabricating IC resistors and compare their performance. (Dec – 14) (10)

Or

With neat sketches describe the various types of integrated resistors. (Dec - 07) (8)

Or

Discuss with neat diagram, the DC characteristics of OP- AMP with necessary expressions. (Nov/Dec 2019) (13)

## **4.3 FABRICATION OF RESISTORS**

$\rightarrow$  The resistors are grouped into two groups: one formed within monolithic and other composed of film resistors.

- $\rightarrow$  The monolithic IC resistors consists suitably dimensioned layers which would form part of the transistor normally.

- $\rightarrow$  Four different methods are available for fabricating integrated resistors namely:

- Diffused resistor

- Epitaxial resistor

- Pinched resistor

- Thin film resistor

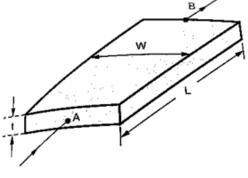

## 4.3.1 Diffused resistor

- $\rightarrow$  If the resistor is formed in one of the isolated regions of epitaxial layer during base or emitter diffusion, then it is called **diffused resistor**.

- $\rightarrow$  It is very economical process as no additional steps in fabrication are needed.

- $\rightarrow$  But the limitation of the diffused resistor is that the range of the value of resistance is very small.

- $\rightarrow$  For larger value of resistor, the larger area of silicon is required.

- $\rightarrow$  Hence the high value resistances are realized by using pinch resistor as shown in the Fig.

- $\rightarrow$  The amount of silicon required for the value of resistor beyond 100 k $\Omega$  is relatively low.

- $\rightarrow$  The accuracy of such resistors is poor. For high value resistors accuracy is not important point to take care.

- $\rightarrow$  It consists of p base layer constricted by an n+ emitter layer, leading to an effective thickness equal to base thickness of an, PN transistor.

Fig 4.3.1 (a) Base resistor

Fig 4.3.1 (b) Emitter resistor

→ As we have already studied that the resistance can be realized by using a defined volume of semiconductor region, consider a sheet of material with length L and Width W as shown in the Fig. Let t be the thickness and  $\rho$  be the uniform resistivity and cross section area A=L\*t.

Sheet resistor

$\rightarrow$  The resistance R between layers A and B is given by,

$$R = \frac{\rho L}{A} = \frac{\rho L}{tW} \tag{1}$$

$\rightarrow$  For square surface area, W = L, then the resistance of the material is given by,

$$R_s = \frac{\rho L}{tL} = \frac{\rho}{t} \tag{2}$$

$\rightarrow$  Thus rearranging equation (1) using equation (2) we can write,

$$R = R_s \left(\frac{L}{W}\right) \tag{3}$$

- $\rightarrow$  Here ratio  $\left(\frac{L}{W}\right)$  is called **aspect ratio**.

- $\rightarrow$  Thus using this technique, base resistor in the range 20  $\Omega$  to 300 k $\Omega$  can be fabricated.

- $\rightarrow$  Similarly the resistance of the emitter diffusion can be fabricated as sheet resistor but the range of resistance is only 10 to 1 k $\Omega$ .

## **4.3.2 EPITAXIAL RESISTOR:**

## Epitaxial resistor

- $\rightarrow$  By using n-epitaxial collector layer, the large value resistances than base and emitter diffusion can be achieved.

- $\rightarrow$  Such resistors are called epitaxial resistors as shown in the Fig. above.

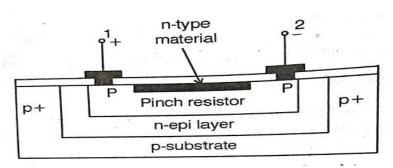

#### **4.3.3 PINCHED RESISTOR**

- → The sheet resistivity of a semiconductor region can be increased by reducing its effective crosssectional area.

- → In pinched resistor, this technique is used to achieve a high value of sheet resistance from the ordinary base diffused resistor.

- $\rightarrow$  It can offer resistance of the order of mega ohms in a smaller area.

- → In this structure no current can flow in the N- type material since the diode realized at contact 2 is biased in the reverse direction.

- → Only smaller reverse saturation current can flow in the N- region. Therefore by forming this N-region in the base diffusion, conduction path for the current has been reduced and pinched.

- → The resistance between the contact 1, 2 increases as the width narrows down and hence it acts as a pinched resistor.

Fig 4.3.3 Pinched resistor

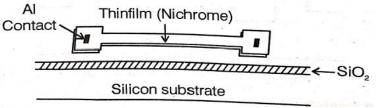

## **4.3.4 THIN FILM RESISTOR**

- $\rightarrow$  In this a very thin metallic film usually of Nichrome (NiCr) of thickness less than 1 µm is vapour deposited on the SiO<sub>2</sub> layer.

- $\rightarrow$  Using masked etching, desired geometry of this thin film is achieved to obtained suitable values of resistors.

- → The ohmic contacts are made using A1 metallization and usual masked etching techniques Nichrome resistors are available with typical sheet resistance values of 40 to 400Ω/ square depending upon film thickness, so the resistance in the range of 20 to 50 kΩ can be obtained.

Fig 4.3.4 Thick film resistor

## 4.3.4.1 Advantages

- → They have lesser and small parasitic components and hence their high frequency behaviour is better.

- $\rightarrow$  The value of resistors can be easily adjusted even after fabrication by cutting a part of resistor with a laser beam.

- $\rightarrow$  They have low temperature coefficient, thereby making them stable.

#### 4.3.4.2 Disadvantages

- $\rightarrow$  Additional steps required in their fabrication process.

- 15. Explain about MOSFET fabrication. Or explain the fabrication of FET in detail. [Apr/May 2019]

## **4.4 FABRICATION OF FET:**

- → The FET is a device in which the flow of current through the conducting region is controlled by an electric field and hence the name Field Effect Transistor (FET).

- $\rightarrow$  Based on the construction, the FETs are classified into 2 types,

- Junction Field Effect Transistor (JFET)

- Metal Oxides Semiconductor Field Effect Transistor (MOSFET)

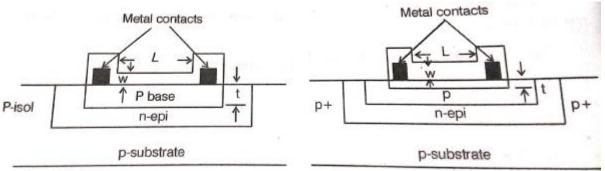

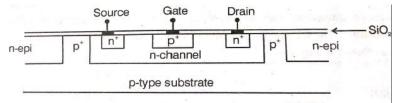

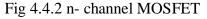

#### 4.4.1 JFET Fabrication

- $\rightarrow$  The basic processes used are the same as in BJT fabrication.

- $\rightarrow$  The epitaxial layer which formed the collector of the BJT is used as n- Channel of JFET.

- $\rightarrow$  The p+ gate is formed in n- channel by the process of ion-implementation or diffusion.

$\rightarrow$  The n+ regions have formed under the source and drain contact regions to provide ohmic contact.

Fig 4.4.1 n- channel JFET

## **4.4.2 Integrated MOSFETs**

- $\rightarrow$  MOSFETS are classified as follows:

- (i) Enhancement mode MOSFET

- ii) Depletion mode MOSFET

- $\rightarrow$  In MOSFETS gate terminal is isolated from the FET channel by silicon dioxide insulating layer.

- $\rightarrow$  As the layer is insulating type, it provides very high input resistance.

- $\rightarrow$  In providing superior barrier for impurities penetrating SiO<sub>2</sub> layer, silicon nitride (Si<sub>3</sub>N<sub>4</sub>) is sandwiched between two silicon dioxide (SiO<sub>2</sub>) layers.

- $\rightarrow$  This helps in increasing overall dielectric constant.

- → The n-channel MOSFET of enhancement and depletion mode are as shown in the Fig. (a) and (b) respectively.

(a) Enhancement

(b) Depletion

- $\rightarrow$  In the enhancement mode MOSFET is in OFF state when gate-source bias is zero while MOSFET turns ON by positive gate source voltage.

- $\rightarrow$  In depletion mode, because of n-implanted channel, conduction is possible in ON state for zero gate source voltage, while negative gate source voltage is required to turn it OFF.

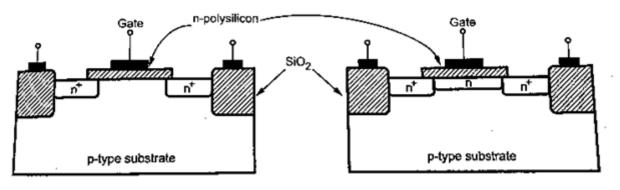

#### (ii) Write a note on CMOS technology.

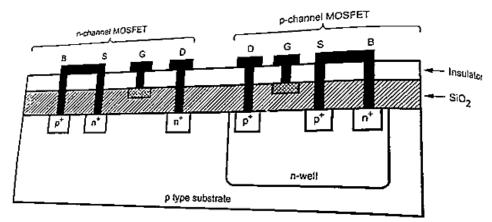

## Or Explain CMOS fabrication with neat sketches. (Dec – 14) (May-18) (13, 8) 4.4.3 FABRICATION OF CMOS:

- → When n-channel MOSFET and p-channel MOSFET both are integrated on same the device is chip, termed as complementary CMOS.

- $\rightarrow$  In CMOS fabrication, n –type well is diffused in p-type substrate.

- $\rightarrow$  Also p-channel MOSFET is fabricated within this n-well.

- $\rightarrow$  Basically this n-well forms substrate for p-channel MOSFET.

- $\rightarrow$  In the fabrication of p-channel MOSFET two additional steps are required as compared to n-channel MOSFET fabrication.

- $\rightarrow$  The additional steps are formation of n-well and ion-implantation of p-type source and drain regions.

- $\rightarrow$  The cross section of CMOS IC is as shown in the Fig.

#### Cross-section of CMOS

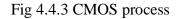

## **4.5 FABRICATION OF PV CELL**

→ A PV cell means photovoltaic cell or solar cell which works on photovoltaic effect. It generates voltage proportional to the light incident on it.

## 4.5.1 Steps of fabrication of PV cell

#### 4.5.1.1 Refining silicon:

- $\rightarrow$  The available mineral in earth is SiO<sub>2</sub>. This is used to obtain silicon by removing oxygen.

- $\rightarrow$  For this it is heated to 1500- 2000 °C in an electrode arc furnace with coal and charcoal i.e., reaction with carbon.

- $\rightarrow$  The silicon obtained is 98% pure which contains the impurities like iron, aluminium etc.

- → To remove these impurities, this silicon reacted with hydrous HCL to obtain SiHCL<sub>3</sub>. Along with hydrogen at 1100 °C to produce pure silicon.

#### <u>4.5.1.2</u>

#### Screen printed PV cell fabrication

**Fig 4.5 Construction**

$\rightarrow$  The first step in this process is to obtain silicon wafer of 10 x 10 sq.cm and 0.5 mm thick. It is then p- type doped so as to obtain p- type wafer.

- $\rightarrow$  The wafer is then heated in a furnace at 800- 1000°C with a phosphorous. This cause small amount of phosphorous to be deposited on the outer layer of silicon.

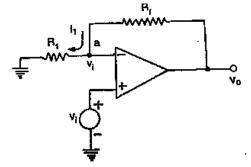

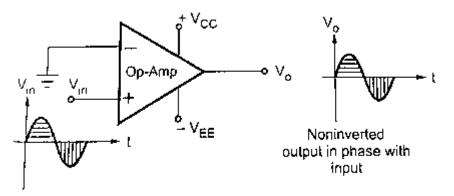

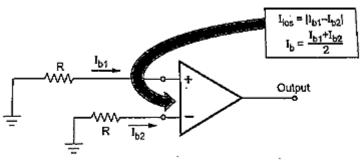

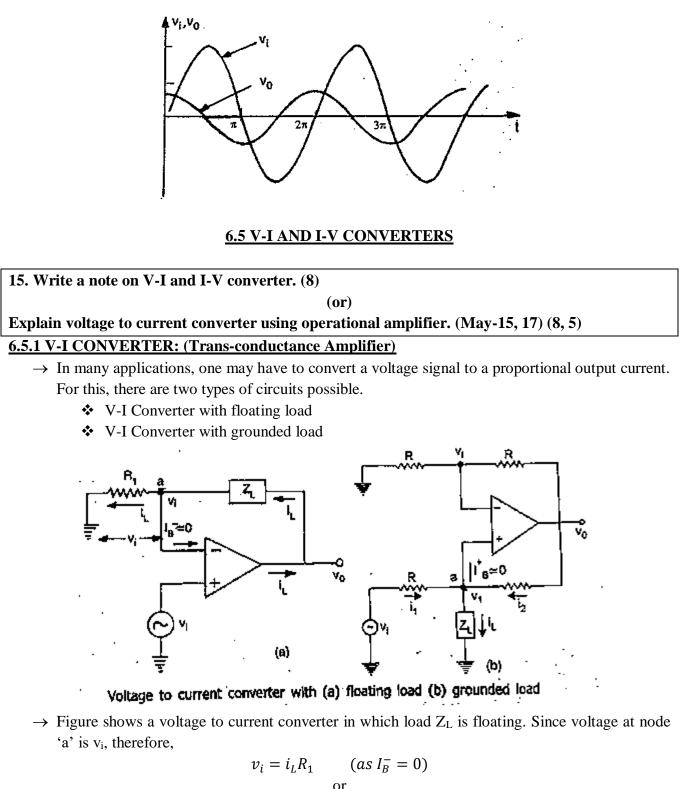

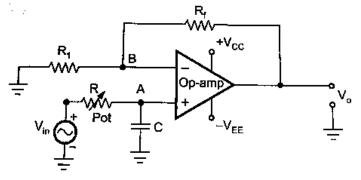

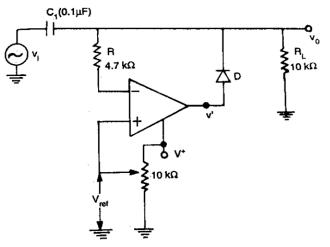

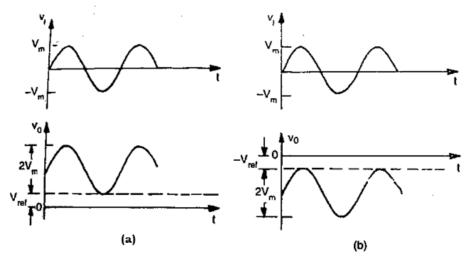

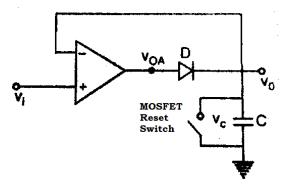

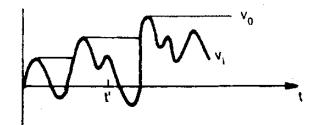

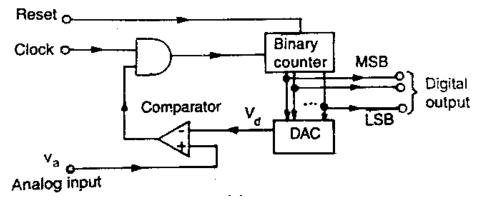

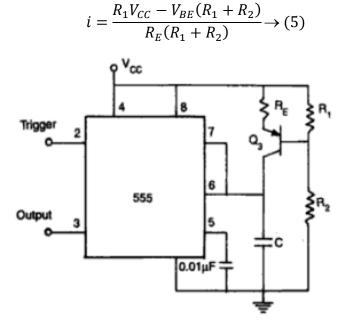

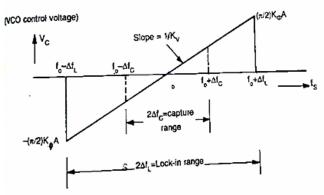

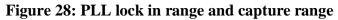

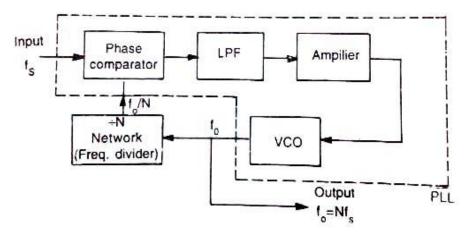

- $\rightarrow$  The phosphorous is required below the screen printed contact to maintain low contact resistance.